- The best anti-Prime Day deals 2025 from Best Buy, Walmart, & more: Top sales from Amazon's competition

- I've tested dozens of wearables and the Apple Watch 10 is one of my favorites - here's why

- Paddle Pays $5m to Settle Tech Support Scam Allegations

- Sony is giving away free 65-inch 4K TVs right now - here's how to qualify for the deal

- Continuous Threat Exposure Management (CTEM): The Future of Vulnerability Assessment

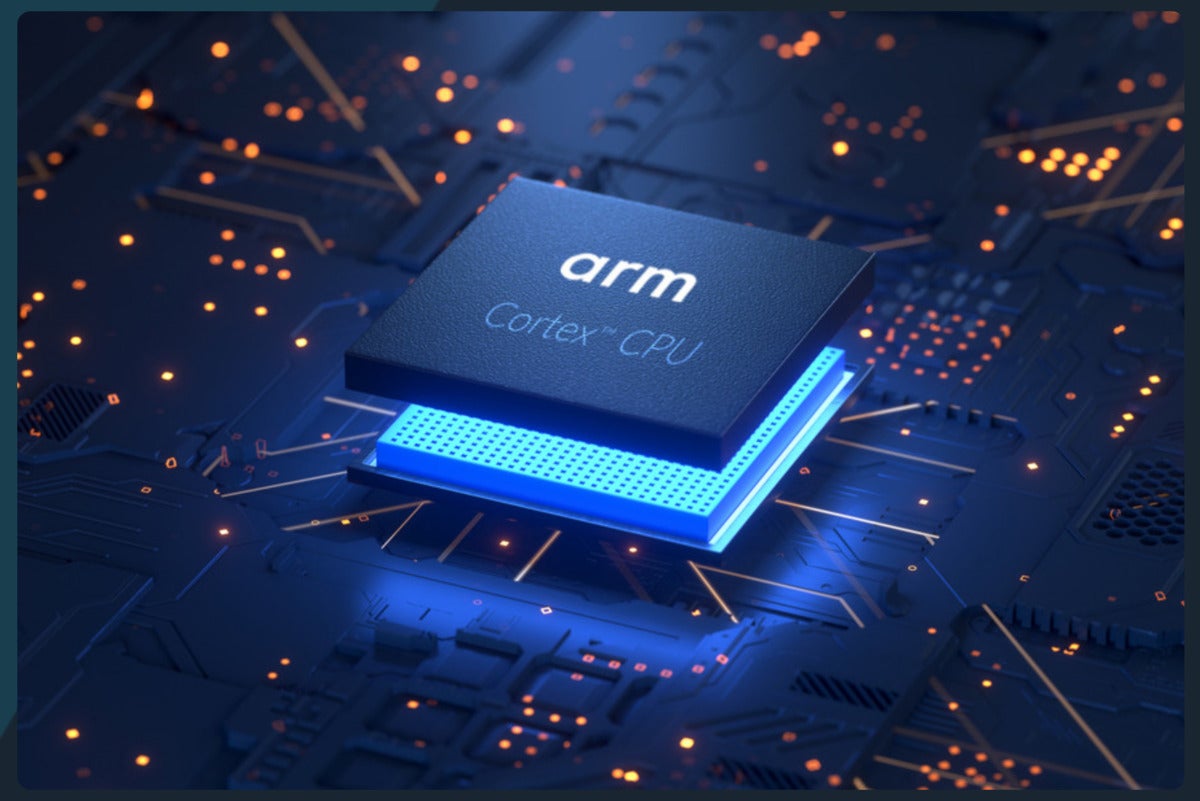

Arm unveils project to rapidly develop server processors

Arm Holdings unveiled a program that it says will simplify and accelerate the adoption of Arm Neoverse-based technology into new compute solutions. The program, called Arm Neoverse Compute Subsystems (CSS), was introduced at the Hot Chips 2023 technical conference held at Stanford University.

Neoverse is Arm’s server-side technology meant for high performance while still offering the power efficiency that Arm’s mobile parts are known for. CSS enables partners to build specialized silicon more affordably and quickly than previous discrete IP solutions.

The first-generation CSS product, Arm CSS N2, is based on the Neoverse N2 platform first introduced in 2020. CSS N2 provides partners with a customizable compute subsystem, allowing them to focus on features like memory, I/O, acceleration, and so on.

Arm doesn’t make chips in the traditional way that Intel and others do. It makes designs, and licensees have to build their own silicon. That often means licensees have to do a lot of work on the plumbing of the processor, then validating it, integrating it, and testing it with whatever custom IP they add to it.

CSS is intended to provide a more complete design, reducing the amount of work that a licensee would have to do on their own. Is intended to make it easier and faster to develop data-center grade processors based on Neoverse designs.

“If we take a step back and look at 2018, when we introduced our Neoverse product line, … a majority of the cloud workloads were running on general-purpose servers. These were general-purpose processors, kind of a one-size-fits-all running all those workloads. And one of the fundamental tenants of our product portfolio was the shift to specialized processing that would be running these sophisticated cloud-native workloads,” Jeff Defilippi, senior director of product management at Arm sa,id on a pre-briefing conference call.

CSS N2 can be configured with anywhere from 24 to 64 cores running at between 2.1GHz and 3.6Ghz, each with 1MB L2 cache and a total 64MB of shared system cache. The design also supports up to eight channels of DDR5 memory and 64 lanes of PCIe 5.0 connectivity. The CSS N2 design is aimed at silicon designs targeted at scale-out clouds, AI applications, 5G kit, data processing units (DPUs/SmartNICs), and networking equipment.

The Arm Neoverse Compute Subsystems is available from Arm Holdings now to anyone looking to build their own custom silicon.

Copyright © 2023 IDG Communications, Inc.