Cisco Silicon One Powers the Next-Generation Enterprise Switches – Cisco Blogs

One of the biggest features of the new Catalyst 9500X and 9600X enterprise switches announced today is the inclusion of Cisco Silicon One Q200 ASICs. Back in 2019 when we introduced the Q100, the first member of the Cisco Silicon One family of devices, we made bold claims about uncompromised performance, efficiency, and flexibility that the architecture that underscores Cisco Silicon One will bring to networking. Today we are demonstrating this is certainly true for campus core switching.

These claims were first validated by shipping products in the form of the Cisco 8000 family of routers that are deployed by service providers, as well as web-scale Datacenter Networks (DCN) and Datacenter Interconnect (DCI) roles, and by the adoption of Cisco Silicon One directly in device form by Mass Scale Data Center (MSDC) operators.

Cisco Silicon One’s clean sheet architecture efficiently caters to different network market segments. Today’s announcement expands Cisco Silicon One to the enterprise network core, delivering on the promise of one architecture covering service provider, web scale, and enterprise networks. Enabling developers and network operators to focus all resources on understanding, qualifying, deploying, and troubleshooting one architecture reduces the cost for both investment and operations. This further reinforces the promise of future expansion of Cisco Silicon One to new roles in these networks while at the same time expanding next generation device performance and value leadership.

These diverse systems and applications take advantage not only of the flexibility of the architecture but also of the diversity of Cisco Silicon One devices available today. There are 11 announced Cisco Silicon One chips at the time of this writing, covering the full range of bandwidth, features, and scale requirements for all networking use cases.

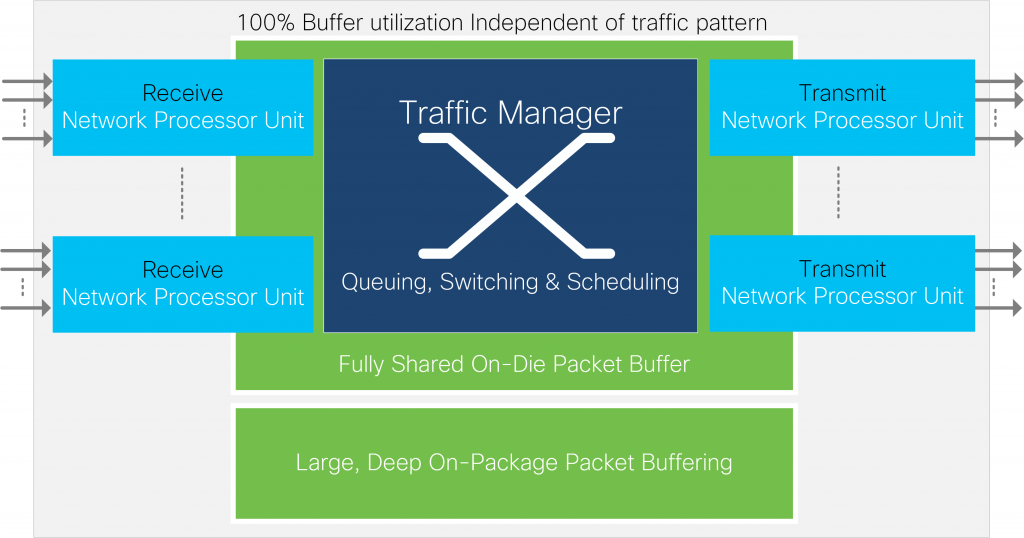

Some might say it’s impossible to efficiently handle such diverse roles with one architecture. However, one architecture doesn’t mean one device, or one implementation of key functionality (e.g., Traffic Manager). What we mean by one architecture is there is a consistent language and work partitioning between different functions across the switching and routing devices. Then, different implementations place greater or lesser emphasis on different functions. For example, one implementation of a traffic manager supports hierarchical QoS with deep buffering, while another handles low latency and power efficiency vs. throughput. By sharing the same architecture, different implementations can be mixed into devices, resulting in a family of devices, each optimized for different roles and all able to work together in a single system.

The two pillars that enable such flexibility and capabilities are the novel Network Processing Unit (NPU) and the Traffic Manager architecture.

Cisco Silicon One employs an NPU built from custom task-optimized processors and hardware-accelerated databases. Implementations differ in the mix of processors, databases, and scale. Programmed in P4 and using a run-to-complete programming model, it enables unprecedented flexibility without compromising efficiency. This is evident by the successful application of the NPU to service provider, datacenter, and now enterprise core and edge roles. Enterprise features such as Cisco TrustSec, Cisco Switched Virtual Links (SVL), QinQ, NAT, and object group ACLs among others are enabled by the programming of the NPU.

Cisco Silicon One Traffic Manager is the other pillar. Employing a fully shared and scalable buffer architecture at its core maximizes the performance extracted from the available on-die buffer resources and optimizes power efficiency while greatly simplifying queuing and scheduling functions. This last point enables Cisco Silicon One to offer service provider-class traffic management at the ‘cost’ of a basic priority-only queueing. The traffic manager furthermore supports both on-die only and hybrid on-die plus DRAM buffering arrangements. By taking advantage of advanced packaging technology, Cisco Silicon One supports both configurations with the same core die.

In summary, the introduction of the Cisco Catalyst 9500X and 9600X based on Cisco Silicon One is yet another testament to delivering on the promise of a converged switching and routing silicon architecture. The new Catalyst 9500X and 9600X switches are the most powerful, most power-efficient campus core switches yet. And being based on Cisco Silicon One also makes them some of the most programmable, future-proof switches available today and well into the future. For more information and ongoing updates, visit the Cisco Silicon One page.

Share: